# S5M8767A

# **Power Management IC for Mobile Applications**

Revision 0.10 December 2011

# si - plaza / Jeff\_cui at 14:14,2011.12.13

# Data Sheet

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or otherwise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

© 2011 Samsung Electronics Co., Ltd. All rights reserved.

### **Important Notice**

Samsung Electronics Co. Ltd. ("Samsung") reserves the right to make changes to the information in this publication at any time without prior notice. All information provided is for reference purpose only. Samsung assumes no responsibility for possible errors or omissions, or for any consequences resulting from the use of the information contained herein.

This publication on its own does not convey any license, either express or implied, relating to any Samsung and/or third-party products, under the intellectual property rights of Samsung and/or any third parties.

Samsung makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Samsung assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation any consequential or incidental damages.

Customers are responsible for their own products and applications. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts.

Samsung products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Samsung product could reasonably be expected to create a situation where personal injury or death may occur. Customers acknowledge and agree that they are solely responsible to meet all other legal and regulatory requirements regarding their applications using Samsung products notwithstanding

#### Copyright © 2011 Samsung Electronics Co., Ltd.

Samsung Electronics Co., Ltd. San #24 Nongseo-Dong, Giheung-Gu Yongin-City, Gyeonggi-Do, Korea 446-711

Contact Us: <u>wonseok.kang@samsung.com</u> TEL: (82)-(31)-209-9287 FAX: (82)-(31)-209-3131

Home Page: http://www.samsungsemi.com

any information provided in this publication. Customer shall indemnify and hold Samsung and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, expenses, and reasonable attorney fees arising out of, either directly or indirectly, any claim (including but not limited to personal injury or death) that may be associated with such unintended, unauthorized and/or illegal use.

WARNING No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior written consent of Samsung. This publication is intended for use by designated recipients only. This publication contains confidential information (including trade secrets) of Samsung protected by Competition Law, Trade Secrets Protection Act and other related laws, and therefore may not be, in part or in whole, directly or indirectly publicized, distributed, photocopied or used (including in a posting on the Internet where unspecified access is possible) by any unauthorized third party. Samsung reserves its right to take any and all measures both in equity and law available to it and claim full damages against any party that misappropriates Samsung's trade secrets and/or confidential information.

**警告** 本文件仅向经韩国三星电子株式会社授权的人员提供, 其内容含有商业秘密保护相关法规规定并受其保护的三星电 子株式会社商业秘密,任何直接或间接非法向第三人披露、 传播、复制或允许第三人使用该文件全部或部分内容的行为 (包括在互联网等公开媒介刊登该商业秘密而可能导致不特 定第三人获取相关信息的行为)皆为法律严格禁止。此等违 法行为一经发现,三星电子株式会社有权根据相关法规对其 采取法律措施,包括但不限于提出损害赔偿请求。

### **Trademarks**

All brand names, trademarks and registered trademarks belong to their respective owners.

- Exynos, Exynos4210, FlexOneNAND, and OneNAND are trademarks of Samsung Electronics.

- ARM, Jazelle, TrustZone, and Thumb are registered trademarks of ARM Limited. Cortex, ETM, ETB, Coresight, ISA, and Neon are trademarks of ARM Limited.

- Java is a trademark of Sun Microsystems, Inc.

- SD is a registered trademark of Toshiba Corporation.

- MMC and eMMC are trademarks of MultiMediaCard Association.

- JTAG is a registered trademark of JTAG Technologies, Inc.

- Synopsys is a registered trademark of Synopsys, Inc.

- I2S is a trademark of Phillips Electronics.

- I<sup>2</sup>C is a trademark of Phillips Semiconductor Corp.

- MIPI and Slimbus are registered trademarks of the Mobile Industry Processor Interface (MIPI) Alliance.

All other trademarks used in this publication are the property of their respective owners.

## **Chip Handling Guide**

#### **Precaution against Electrostatic Discharge**

When handling semiconductor devices, be sure that the environment is protected against static electricity.

- 1. Operators should wear anti-static clothing and use earth band.

- 2. All objects that come in direct contact with devices should be made of materials that do not produce static electricity that would cause damage.

- 3. Equipment and work table must be earthed.

- 4. Ionizer is recommended to remove electron charge.

#### Contamination

Be sure to use semiconductor products in the environment that may not be exposed to dust or dirt adhesion.

#### **Temperature/Humidity**

Semiconductor devices are sensitive to environment temperature and humidity. High temperature or humidity may deteriorate semiconductor device's characteristics. Therefore avoid storage or use in such conditions.

#### **Mechanical Shock**

Care should be exercised not to apply excessive mechanical shock or force on semiconductor device.

#### Chemical

Do not expose semiconductor device to chemical because reaction to chemical may cause deterioration of device characteristics.

#### **Light Protection**

In case of non-EMC (Epoxy Molding Compound) package, do not expose semiconductor IC to strong light. It may cause device's malfunction. (But, some special products which utilize the light or have security function are excepted from this guide)

#### Radioactive, Cosmic and X-ray

Semiconductor devices can be influenced by radioactive, cosmic ray or X-ray. Radioactive, cosmic and X-ray may cause soft error during device operation. Therefore semiconductor devices must be shielded under environment that may be exposed to radioactive, cosmic ray or X-ray.

#### EMS (Electromagnetic Susceptibility)

Note that semiconductor device's characteristics may be affected by strong electromagnetic wave or magnetic field during operation under insufficient PCB circuit design for EMS.

#### SAMSUNG ELECTRONICS

## **Revision History**

| Revision No. | Date         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Author(s) |

|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 0.00         | Nov. 9, 2011 | Released Initial preliminary specification                                                                                                                                                                                                                                                                                                                                                                                                                                      | WS Kang   |

| 0.10         | Dec.5, 2011  | <ul> <li>Ordering information is changed.</li> <li>LDO4 is modified default on and added to power sequence.</li> <li>Buck9 default voltage is changed.</li> <li>Figure3 System Connection Diagram is modified.</li> <li>Description of Manual reset function is modified.</li> <li>Buck Remote Sense description is updated.</li> <li>Mode control description of LDO4/18/23 is added.</li> <li>Table3 is modified.</li> <li>Slave address of PM section is updated.</li> </ul> | WS Kang   |

## **Table of Contents**

| 1 PRODUCT OVERVIEW                                                                    | 11     |

|---------------------------------------------------------------------------------------|--------|

| 1.1 Introduction                                                                      |        |

| 1.2 Features                                                                          |        |

| 1.2.1 Regulators                                                                      | 12     |

| 1.2.2 Supplementary Functions                                                         | 13     |

| 1.2.3 Applications                                                                    | 13     |

| 1.2.4 Ordering Information                                                            |        |

| 1.3 Block Diagram                                                                     |        |

| 1.4 Ball Configuration (Top View)                                                     |        |

| 1.5 Ball Description                                                                  |        |

| 1.6 Absolute Maximum Ratings                                                          |        |

| 1.7 Recommended Operating Condition                                                   | 22     |

| 2 ELECTRICAL SPECIFICATIONS                                                           | 23     |

| 2.1 General and Logic                                                                 |        |

| 2.2 Buck Converters                                                                   |        |

| 2.2.1 Buck Converter 1, 3, 5, 6, 7, 8, 9                                              |        |

| 2.2.2 Buck Converter 2 & 4                                                            |        |

| 2.3 LDOs                                                                              |        |

| 2.3.1 LDO (P) 4, 5, 11, 12, 13, 14, 16, 17, 19, 20, 21, 22, 26, 27, 28 (150 mA, PMOS) |        |

| 2.3.2 LDO (P) 3, 10, 18, 23, 24, 25 (300 mA, PMOS)                                    |        |

| 2.3.3 LDO (P) 9 (400 mA, PMOS)<br>2.3.4 LDO (N) 1, 6, 7, 15 (150 mA, NMOS)            | <br>20 |

| 2.3.4 LDO (N) 1, 0, 7, 13 (130 MA, NMOS)                                              |        |

| 2.3.5 LDO (N) 8 (300 mA, NMOS)                                                        |        |

| 2.4 Backup Coin Battery Charger                                                       |        |

| 2.5 Clock and RTC                                                                     |        |

| 3 FUNCTIONAL DESCRIPTION                                                              | 49     |

| 3.1 Power Sequence                                                                    | 49     |

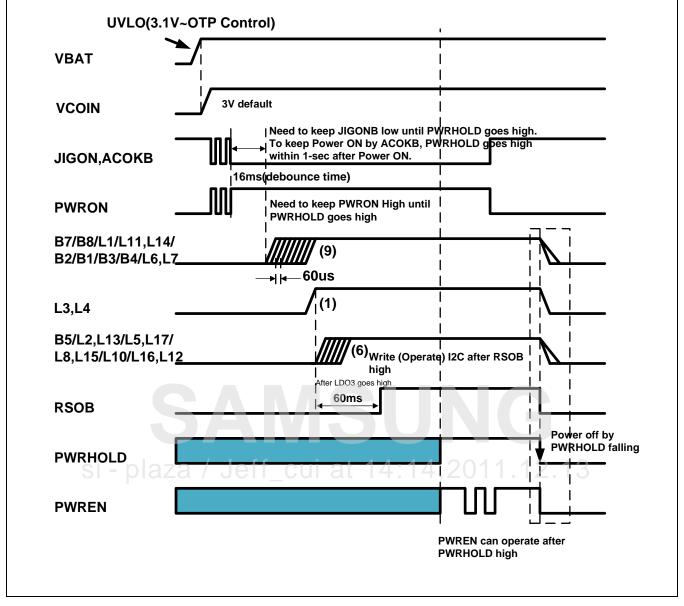

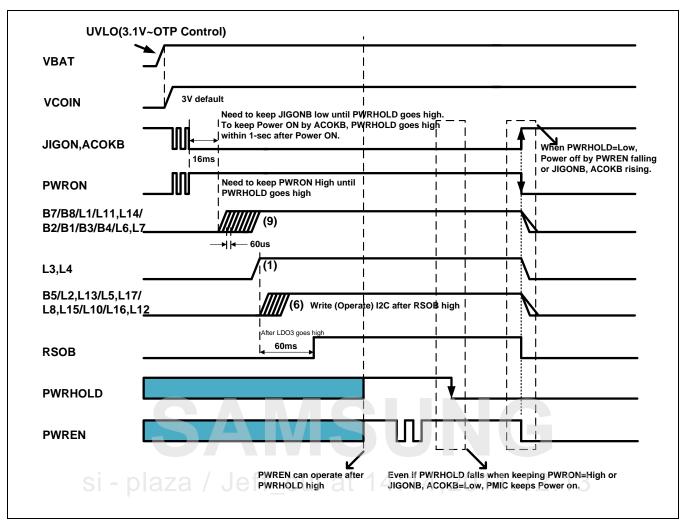

| 3.1.1 Power On Sequence                                                               | 49     |

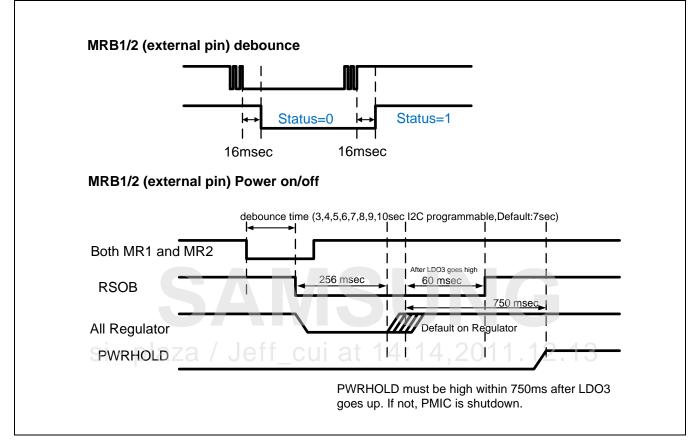

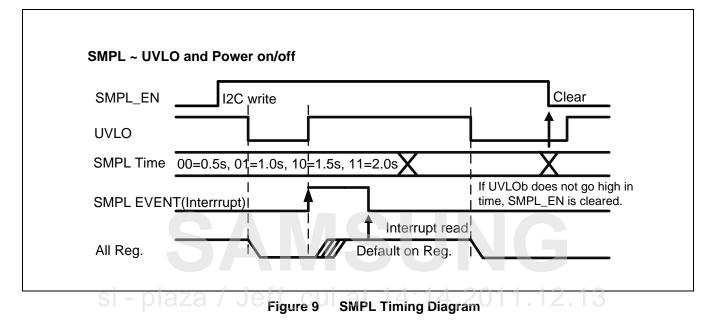

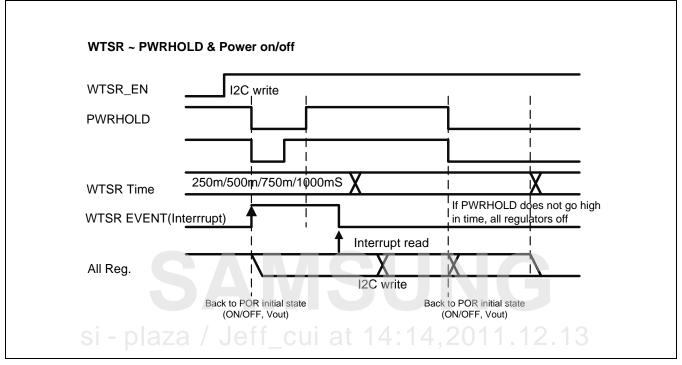

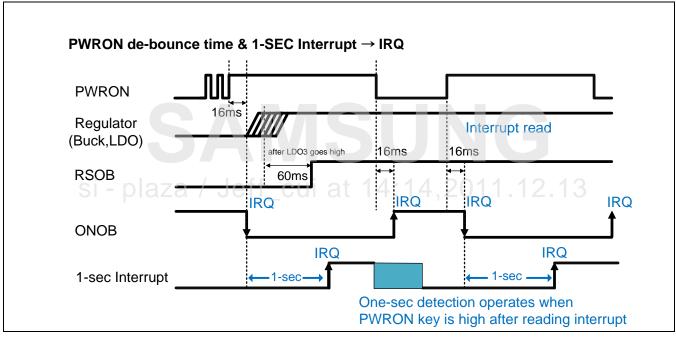

| 3.1.2 MR, SMPL, WTSR, RTC, POR, IRQB                                                  |        |

| 3.2 UVLO, Reference Voltage, Thermal Shutdown                                         |        |

| 3.3 Regulator                                                                         |        |

| 3.3.1 Buck Converters                                                                 |        |

| 3.3.2 LDOs                                                                            |        |

| 3.4 Backup Coin Battery<br>3.4.1 Backup Coin Battery                                  |        |

|                                                                                       |        |

| 4 DIGITAL INTERFACE (I2C)                                                             |        |

| 4.1 Slave Address                                                                     |        |

| 4.2 Register Address                                                                  |        |

| 4.2.1 I2C Interface                                                                   |        |

| 4.2.2 Control Interface using SCL (Clock) and SDA (Data)                              |        |

| 4.2.3 I2C Interface Timing Diagram                                                    |        |

| 5 REGISTER DESCRIPTION     | 75  |

|----------------------------|-----|

| 5.1 Power Management       |     |

| 5.1.1 Register Map Summary |     |

| 5.1.2 Bit Map Summary      | 79  |

| 5.2 RTC                    |     |

| 5.2.1 Register Map Summary |     |

| 5.2.2 Bit Map Summary      | 114 |

| 6 APPLICATION CIRCUIT      |     |

| 6.1 Package Dimension      | 128 |

# List of Figures

#### Figure Number

#### Title

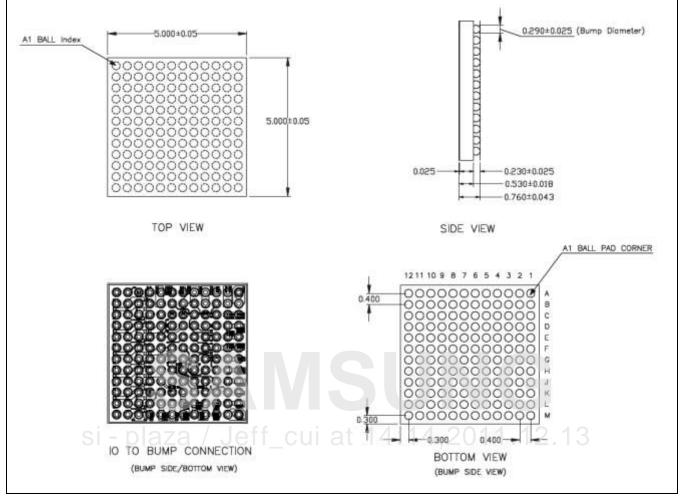

| Figure 1  | S5M8767A Package Top and Bottom Views                                       | 11  |

|-----------|-----------------------------------------------------------------------------|-----|

| Figure 2  | Block Diagram of S5M8767A                                                   |     |

| Figure 3  | System Connection Diagram                                                   |     |

| Figure 4  | Ball Configuration                                                          |     |

| Figure 5  | Power On Sequence                                                           |     |

| Figure 6  | Power on/off Sequence                                                       |     |

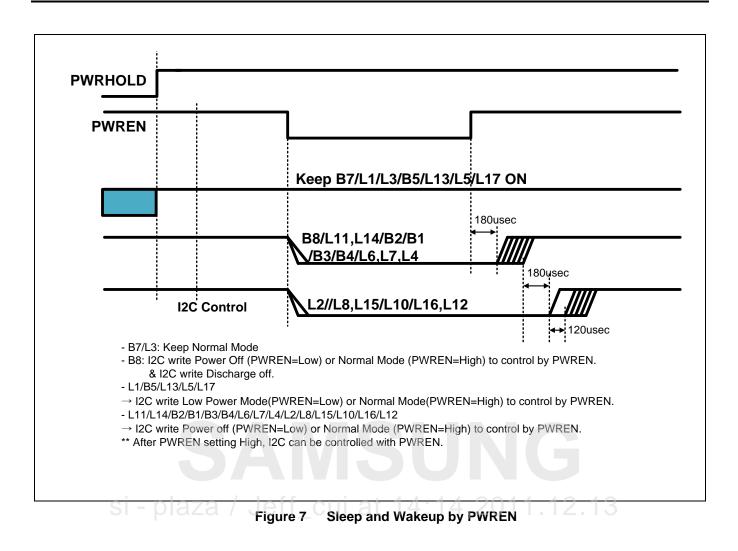

| Figure 7  | Sleep and Wakeup by PWREN                                                   |     |

| Figure 8  | Manual Reset Sequence Timing Diagram                                        |     |

| Figure 9  | SMPL Timing Diagram                                                         |     |

| Figure 10 | WTSR Timing Diagram                                                         |     |

| Figure 11 | Power On Debounce and Interrupt                                             |     |

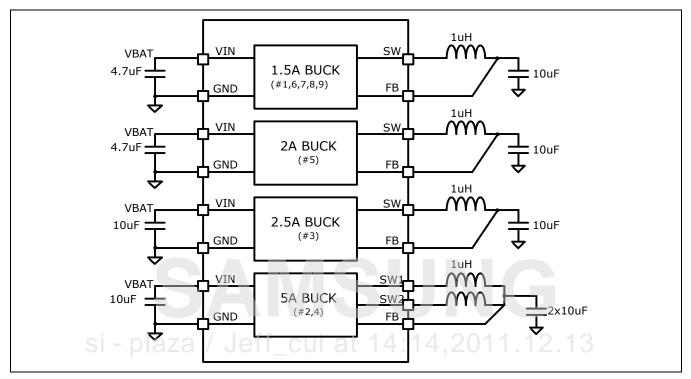

| Figure 12 | Buck Converter Block Diagram                                                |     |

| Figure 13 | Power On Sequence in Buck Converter                                         |     |

| Figure 14 | Buck2/3/4 DVS Control                                                       |     |

| Figure 15 | Remote Sense Pin Connection                                                 |     |

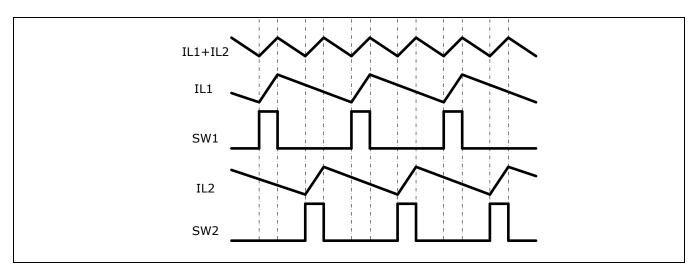

| Figure 16 | SW Node Voltage and Inductor Current Waveforms in Dual Phase Buck Converter | 61  |

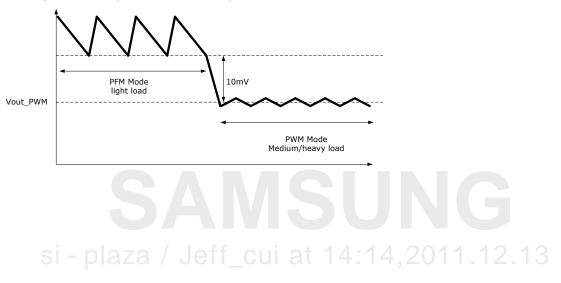

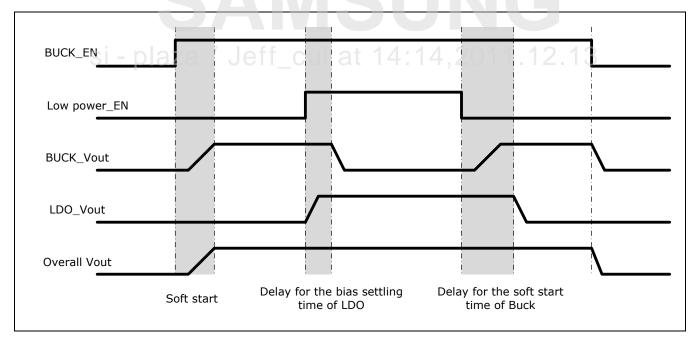

| Figure 17 | Mode Transition Waveforms in Buck 5                                         | 61  |

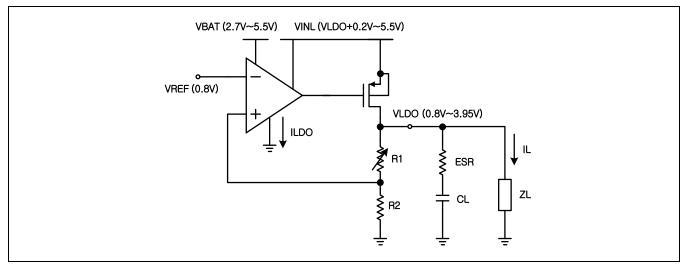

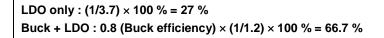

| Figure 18 | PLDO (Low-Dropout Regulator having a PMOS Power Transistor)                 | 64  |

| Figure 19 | Application Example                                                         | 65  |

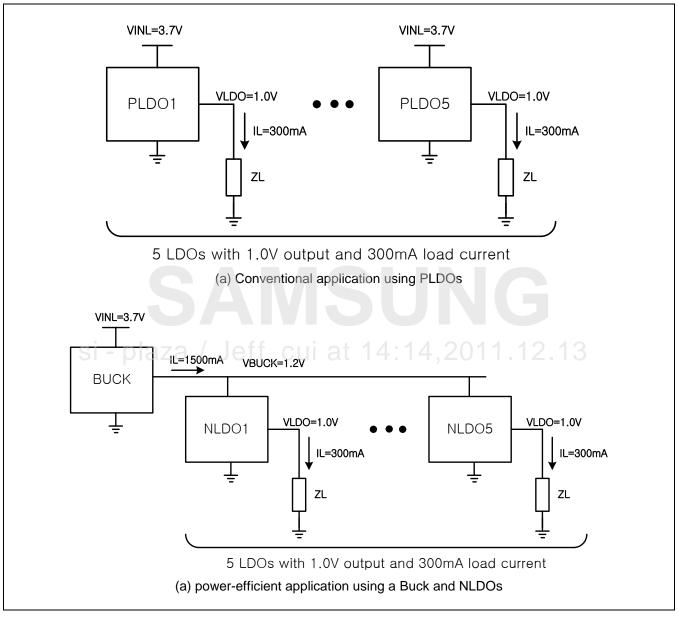

| Figure 20 | NLDO (Low-Dropout Regulator having a NMOS Power Transistor)                 | 66  |

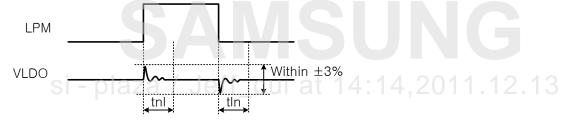

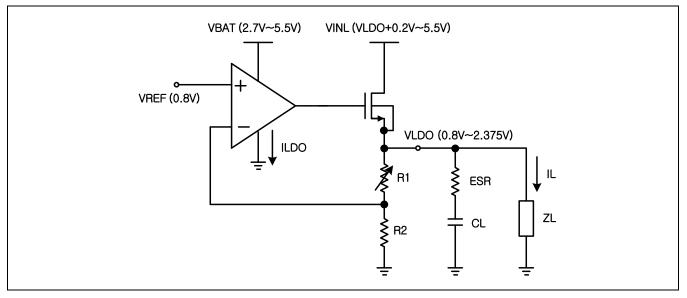

| Figure 21 | Mode Control Waveforms in LDO4, LDO18 and LDO 23                            | 67  |

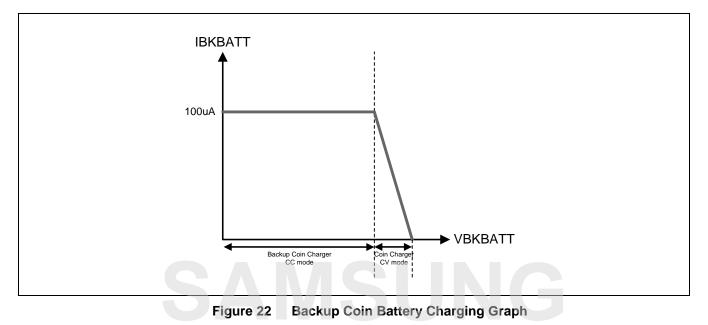

| Figure 22 | Backup Coin Battery Charging Graph                                          | 69  |

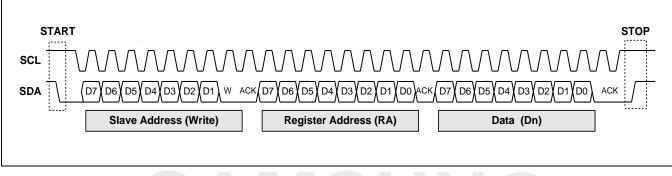

| Figure 23 | Single Byte Write Mode                                                      | 71  |

| Figure 24 | Multi Bytes Write Mode                                                      | 71  |

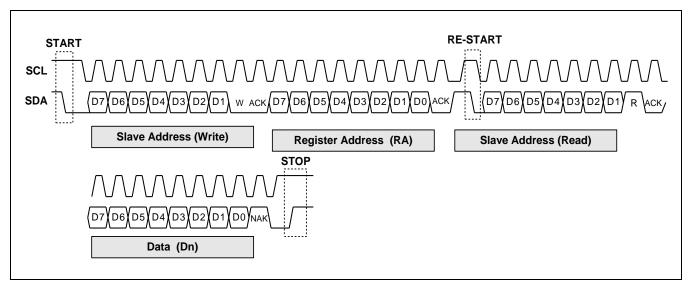

| Figure 25 | Single Byte Read Mode                                                       | 72  |

| Figure 26 | Multi Bytes Read Mode                                                       | 72  |

| Figure 27 | I2C Control Interface Timing Diagram                                        | 73  |

| Figure 28 | Typical Application Circuit                                                 |     |

| Figure 29 | Package Dimension                                                           | 128 |

### **List of Tables**

| Table<br>Number | Title                                   | Page<br>Number |

|-----------------|-----------------------------------------|----------------|

| Number          |                                         | Number         |

|                 | List of Recommended Inductors           |                |

| Table 2         | List of Recommended Capacitors          | 63             |

|                 | Information of Power Supply on Each LDO |                |

| Table 4         | I2C Electrical Specification            | 74             |

|                 | Voltage Table for BUCK 2/3/4            |                |

|                 | Voltage Table for BUCK1/5/6             |                |

|                 | Voltage Table for BUCK7/8/9             |                |

# si - plaza / Jeff\_cui at 14:14,2011.12.13

# List of Conventions

#### **Register RW Access Type Conventions**

| Туре | Definition   | Description                                                                                                                                             |

|------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| R    | Read Only    | The application has permission to read the Register field. Writes to read-only fields have no effect.                                                   |

| W    | Write Only   | The application has permission to write in the Register field.                                                                                          |

| RW   | Read & Write | The application has permission to read and writes in the Register field. The application sets this field by writing 1'b1 and clears it by writing 1'b0. |

| RC   | Read & Clear | If reading 0x01 to 0x03 registers, the information is automatically cleared.                                                                            |

|      |              |                                                                                                                                                         |

#### **Register Value Conventions**

| Description                                        |

|----------------------------------------------------|

| Undefined bit                                      |

| Undefined multiple bits                            |

| Undefined, but depends on the device or pin status |

| The value depends on the device                    |

| The value depends on the pin status                |

|                                                    |

#### **Reset Value Conventions**

| Expression | Description |

|------------|-------------|

| 0          |             |

| 1          |             |

| х          |             |

**Warning:** Some bits of control registers are driven by hardware or write only. As a result the indicated reset value and the read value after reset might be different.

#### 1.1 Introduction

S5M8767A is an advanced Power Management IC (PMIC) designed for mobile applications. It is comprised of high efficient Buck converters including Dual-Phase Buck converters, various LDOs, and an RTC integrated into a 144-WFP (Wafer-level Fabricated Package), 5.0mm × 5.0mm package.

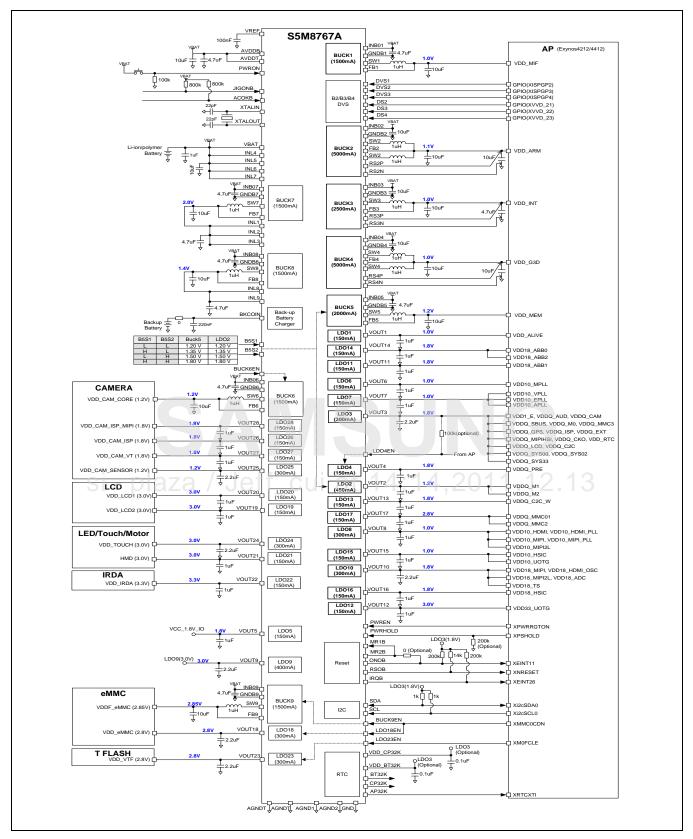

S5M8767A, coupled with Multi Core Samsung Application Processors (Exynos4212/4412/5250), is used in wide mobile applications such as smart phones and tablet PCs.

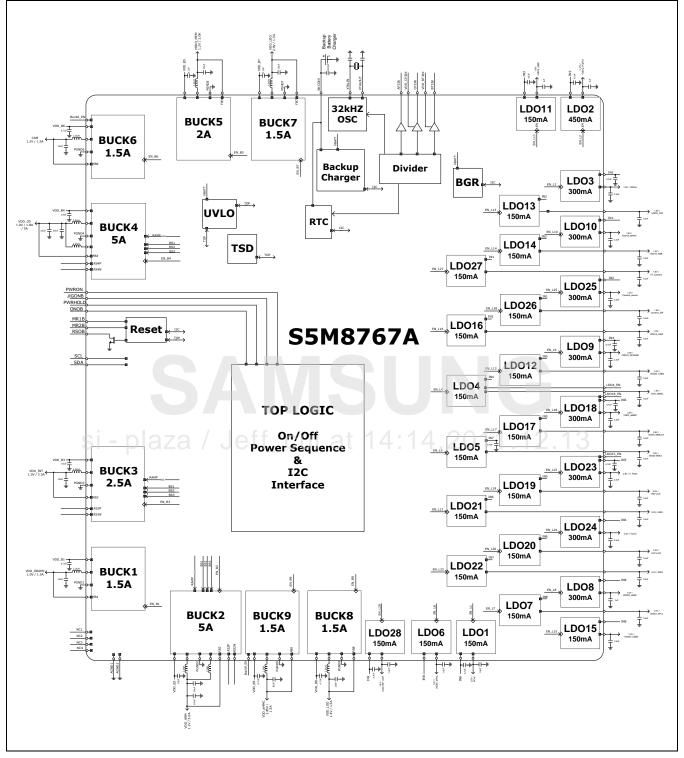

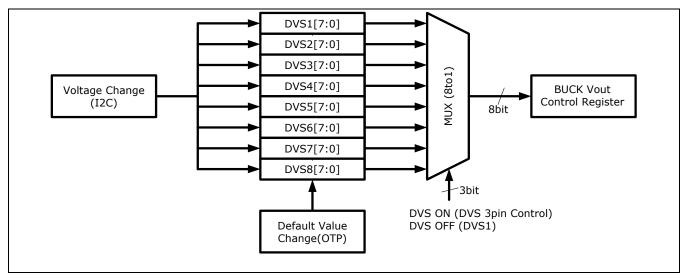

The Buck Converters in S5M8767A provide stable power to the ARM core/cache, internal logic, memory, camera processor, and sub-regulations. Three Buck Converters for high load capacity in Application Processor side also provide optimal power control using Dynamic Voltage Scaling (DVS) via I2C or GPIO interface between PMIC and Application Processor.

The various LDOs supply appropriate power to each I/O and functional block in an Application Processor and camera IC in set application. Applying independent LDO to each I/O block helps the CPU to support various types of devices. Each block can be turned on and turned off for power optimization. Other features include thermal regulation and internal timer function.

Figure 1 S5M8767A Package Top and Bottom Views

#### SAMSUNG ELECTRONICS

#### 1.2 Features

The key features of S5M8767A include:

#### 1.2.1 Regulators

- 9 High-Efficiency and programmable Buck Converters (2 Dual Phase Bucks)

- Buck1 (VDD\_MIF): 1.5 A (0.65 V to 2.225 V, 6.25mV step, default on 1.0 V)

- Buck2 (VDD\_ARM): 5.0 A, Eight Step DVS (0.6 V to 1.6 V, 6.25 mV step, default on 1.1 V)

- Buck3 (VDD\_INT): 2.5 A, Eight Step DVS (0.6 V to 1.6 V, 6.25 mV step, default on 1.0 V)

- Buck4 (VDD\_G3D): 5.0 A, Eight Step DVS (0.6 V to 1.6 V, 6.25 mV step, default on 1.0 V)

- Buck5 (VDD\_MEM): 2.0 A (0.65 V to 2.225 V, 6.25 mV step, default on 1.2 V), supports low power mode at sleep state

- Buck6 (VDD\_CAM\_CORE): 1.5 A (0.65 V to 2.225 V, 6.25 mV step, default off 1.2 V)

- Buck7 (VDD\_H\_LDO): 1.5 A (0.75 V to 3.0 V, 12.5 mV step, default on 2.0 V)

- Buck8 (VDD\_L\_LDO): 1.5 A (0.75 V to 3.0 V, 12.5 mV step, default on 1.4 V)

- Buck9 (VDD F\_eMMC): 1.5 A (0.75 V to 3.3 V, 12.5 mV step, default off 2.85 V)

- 28 LDO Regulators (22 PMOS LDOs, 6 NMOS LDOs, N:NMOS type LDO, P:PMOS type LDO)

- LDO1 (N): 150 mA (0.8 V to 2.375 V, 25 mV step, default on 1.0 V)

- LDO2 (N): 450 mA (0.8 V to 2.375 V, 25 mV step, default on 1.2 V)

- LDO3 (P): 300 mA (0.8 V to 3.95 V, 50 mV step, default on 1.8 V)

- LDO4 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default on 1.8 V)

- LDO5 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default on 1.8 V)

- LDO6 (N): 150 mA (0.8 V to 2.375 V, 25 mV step, default on 1.0 V)

- LDO7 (N): 150 mA (0.8 V to 2.375 V, 25 mV step, default on 1.0 V)

- LDO8 (N): 300 mA (0.8V to 2.375 V, 25 mV step, default on 1.0 V)

- LDO9 (P): 400 mA (0.8 V to 3.95 V, 50 mV step, default off 3.0 V)

- LDO10 (P): 300 mA (0.8 V to 3.95 V, 50 mV step, default on 1.8 V)

- LDO11 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default on 1.8 V)

- LDO12 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default on 3.0 V)

- LDO13 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default on 1.8 V)

- LDO14 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default on 1.8 V)

- LDO15 (N): 150 mA (0.8 V to 2.375 V, 25 mV step, default on 1.0 V)

- LDO16 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default on 1.8 V)

- LDO17 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default on 2.8 V)

- LDO18 (P): 300 mA (0.8V to 3.95 V, 50 mV step, default off 2.8 V)

- LDO19 (P): 150 mA (0.8V to 3.95 V, 50 mV step, default off 3.0 V)

- LDO20 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default off 3.0 V)

- LDO21 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default off 3.0 V)

- LDO22 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default off 3.3 V)

SAMSUNG ELECTRONICS

- LDO23 (P): 300 mA (0.8 V to 3.95 V, 50 mV step, default off 2.8 V)

- LDO24 (P): 300 mA (0.8 V to 3.95 V, 50 mV step, default off 3.0 V)

- LDO25 (P): 300 mA (0.8 V to 3.95 V, 50 mV step, default off 1.2 V)

- LDO26 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default off 1.8 V)

- LDO27 (P): 150 mA (0.8 V to 3.95 V, 50mV step, default off 1.8 V)

- LDO28 (P): 150 mA (0.8 V to 3.95 V, 50 mV step, default off 1.8 V)

#### **1.2.2 Supplementary Functions**

- RTC with two alarms

- Three Buffered 32.768 kHz Outputs (for AP, CP, and B/T)

- One Back up battery charger

- Low-Battery Monitor and Reset Output

- Under Voltage Lock Out / Thermal Shutdown / BandGap Reference

- Power-on Sequence

- I2C Interface for Programming

#### 1.2.3 Applications

- Smart Phones and Cellular Phones

- Portable Applications (Tablet PC and Wireless Handheld)

# i - plaza / Jeff\_cui at 14:14,2011.12.13

#### **1.2.4 Ordering Information**

| Device                 | Package                               | Operating Temperature |  |  |

|------------------------|---------------------------------------|-----------------------|--|--|

| S5M8767A01-6030 (NOTE) | 144 WFP – 5.0mm × 5.0mm (0.4mm pitch) | – 40°C to 85°C        |  |  |

**NOTE:** Under Development

**Warning:** This device should be shorted together or the device should be placed in conductive foam during storage or handling to prevent electrostatic damage.

#### SAMSUNG ELECTRONICS

#### 1.3 Block Diagram

Figure 2 Block Diagram of S5M8767A

SAMSUNG ELECTRONICS

14

Figure 3 System Connection Diagram

٦

#### 1.4 Ball Configuration (Top View)

| r | 1         | 2         | 3         | 4           | 5         | 6             | 7           | 8             | 9             | 10      | 11         | 12         |

|---|-----------|-----------|-----------|-------------|-----------|---------------|-------------|---------------|---------------|---------|------------|------------|

| А | NC        | SW6       | GNDB<br>6 | GNDB<br>5   | SW5       | VINB7         | SW7         | GNDB<br>7     | XTALI         | VBAT    | VREF       | NC         |

| в | VINB6     | VINB4     | FB6       | GNDB<br>5   | FB5       | VINB5         | (FB7)       | VDD_<br>BT32K | (XTAL<br>OUT) | (VINL1) | VLDO<br>26 | VLDO<br>3  |

| с | VINB4     | VINB4     | (FB4)     | AGND        | DVS1      | VDD_<br>CP32K | BKCOI       | СР32К         | AP32K         | VINL2   | VLDO<br>27 | VLDO<br>10 |

| D | SW41      | SW41      | RS4P      | AVDD<br>T   | DVS2      | ACOK          | ВТ32К       | VLDO<br>16    | VLDO<br>28    | VINL3   | VLDO<br>13 | VLDO<br>25 |

| Е | SW42      | SW42      | RS4N      | PWRE        | DVS3      | SCL           | PWRON       | VLDO<br>14    | VLDO<br>11    | VINL4   | VLDO<br>4  | VLDO<br>9  |

| F | GNDB<br>4 | GNDB<br>4 | GNDB<br>4 | ONOB        | RSOB      | SDA           | JIGON<br>B  | VLDO<br>19    | VLDO<br>12    | VINL5   | VLDO<br>17 | VLDO<br>23 |

| G | GNDB<br>3 | GNDB<br>3 | FB3       | IRQB        | MR1B      | MR2B          | LDO18<br>EN | VLDO<br>24    | VLDO<br>21    | VINL6   | VLDO<br>20 | VLDO<br>18 |

| н | SW3       | SW3       | (RS3P)    | PWRH<br>OLD | GND       | GND           | (LDO4<br>EN | VLDO<br>5     | VLDO<br>22    | VINL7   | (VLDO<br>1 | VLDO<br>8  |

| J | VINB3     | VINB3     | (RS3N)    | AVDD<br>B   | AGND<br>B | BUCK<br>6EN   | LDO23<br>EN | VLDO<br>6     | VLDO<br>15    | VINL8   | VLDO<br>7  | VLDO<br>2  |

| к | GNDB<br>1 | (FB1)     | FB2       | RS2P        | RS2N      | GNDB<br>2     | DS3         | DS4           | B5S1          | B5S2    | AGND       | VINL9      |

| L | SW1       | VINB2     | VINB2     | SW21        | SW22      | GNDB<br>2     | DS2         | BUCK<br>9EN   | (FB9          | FB8     | AGND       | GNDB<br>8  |

| М | NC        | VINB1     | VINB2     | SW21        | SW22      | GNDB<br>2     | GNDB<br>9   | SW9           | VINB9         | VINB8   | SW8        | NC         |

|   |           |           |           |             |           |               |             |               |               |         |            |            |

Figure 4 Ball Configuration

#### SAMSUNG ELECTRONICS

SAMSUNG

#### **1.5 Ball Description**

| Pin No.                          | Symbol    | I/O   | Description                                                        |  |  |

|----------------------------------|-----------|-------|--------------------------------------------------------------------|--|--|

| Power Management and I2C Section |           |       |                                                                    |  |  |

| A9                               | XTALIN    | AI    | 32.768 kHz Crystal Oscillator Input. Connect 22 pF                 |  |  |

| B8                               | VDD_BT32K | Power | Power Supply for 32.768 kHz BT Buffer                              |  |  |

| B9                               | XTALOUT   | AO    | 32.768 kHz Crystal Oscillator Output. Connect 22 pF                |  |  |

| C4                               | AGNDT     | GND   | Analog Ground for Bucks.                                           |  |  |

| C6                               | VDD_CP32K | Power | Power Supply for 32.768 kHz CP Buffer                              |  |  |

| C7                               | BKCOIN    | AO    | Back up Battery Charger Output                                     |  |  |

| C8                               | CP32K     | DO    | 32.768 kHz Output for CP                                           |  |  |

| C9                               | AP32K     | DO    | 32.768 kHz Output for AP                                           |  |  |

| D4                               | AVDDT     | Power | Power Supply for Bucks.                                            |  |  |

| D6                               | ACOKB     | DI    | VDCIN okay signal from external charger                            |  |  |

| D7                               | BT32K     | DO    | 32.768 kHz Output for BT                                           |  |  |

| E4                               | PWREN     | DI    | Power Enable Pin for Buck2/3/4 and LDO2/6/7/8/10/11/12/14/15/16    |  |  |

| E6                               | SCL       | DI    | I2C Serial Clock Input                                             |  |  |

| E7                               | PWRON     | DI    | Power Enable Signal. Connected 800 k $\Omega$ Pull-down to Ground. |  |  |

| F4                               | ONOB      | DO    | PWRON key active low signal. NMOS Open Drain                       |  |  |

| F5                               | RSOB      | DO    | Reset Output. NMOS Open Drain                                      |  |  |

| F6                               | SDA       | DIO   | I2C Serial Data Bidirectional                                      |  |  |

| F7                               | JIGONB    | DI/   | Power Enable Signal through JIG.                                   |  |  |

| G4                               | IRQB      | DO    | Interrupt Request Output (active low). NMOS Open Drain             |  |  |

| G5                               | MR1B      | DI    | Manual Reset Input 1                                               |  |  |

| G6                               | MR2B      | DI    | Manual Reset Input 2                                               |  |  |

| G7                               | LDO18EN   | DI    | LDO18 Enable                                                       |  |  |

| H4                               | PWRHOLD   | DI    | Power Supply Hold Signal                                           |  |  |

| H5                               | GND       | GND   | Ground                                                             |  |  |

| H6                               | GND       | GND   | Ground                                                             |  |  |

| H7                               | LDO4EN    | DI    | LDO4 Enable                                                        |  |  |

| J4                               | AVDDB     | Power | Power Supply for Bucks.                                            |  |  |

| J5                               | AGNDB     | GND   | Analog Ground for Bucks.                                           |  |  |

| J6                               | BUCK6EN   | DI    | BUCK 6 Enable                                                      |  |  |

| J7                               | LDO23EN   | DI    | LDO23 Enable                                                       |  |  |

| K9                               | B5S1      | DI    | Set the Buck 5 & LDO2 default voltage.                             |  |  |

| K10                              | B5S2      | DI    | Set the Buck 5 & LDO2 default voltage.                             |  |  |

| K11                              | AGND      | GND   | Analog Ground                                                      |  |  |

| L8                               | BUCK9EN   | DI    | BUCK 9 Enable                                                      |  |  |

SAMSUNG ELECTRONICS

| Pin No. | Symbol         | I/O    | Description                                         |  |  |

|---------|----------------|--------|-----------------------------------------------------|--|--|

| L11     | AGND           | GND    | Analog Ground                                       |  |  |

| A1      | NC             | AIO    | No Connection                                       |  |  |

| A12     | NC             | AIO    | No Connection                                       |  |  |

| M1      | NC             | AIO    | No Connection                                       |  |  |

| M12     | NC             | AIO    | No Connection                                       |  |  |

| LDO Reg | ulator, BGR Se | ection |                                                     |  |  |

| B10     | VINL1          | Power  | Power Supply for LDO3/10/26/27 from Buck 7 or VBAT  |  |  |

| C10     | VINL2          | Power  | Power Supply for LDO13/16/25/28 from Buck 7 or VBAT |  |  |

| D10     | VINL3          | Power  | Power Supply for LDO11/14 from Buck7 or VBAT        |  |  |

| E10     | VINL4          | Power  | Power Supply for LDO4/9                             |  |  |

| F10     | VINL5          | Power  | Power Supply for LDO12/17/19/23                     |  |  |

| G10     | VINL6          | Power  | Power Supply for LDO18/20/21/24                     |  |  |

| H10     | VINL7          | Power  | Power Supply for LDO5/22                            |  |  |

| J10     | VINL8          | Power  | Power Supply for LDO1/6/7/8/15 from Buck 8 or VBAT  |  |  |

| K12     | VINL9          | Power  | Power Supply for LDO2 from Buck 8 or VBAT           |  |  |

| H11     | VLDO1          | AO     | LDO1 Output                                         |  |  |

| J12     | VLDO2          | AO     | LDO2 Output                                         |  |  |

| B12     | VLDO3          | AO     | LDO3 Output                                         |  |  |

| E11     | VLDO4          | AO     | LDO4 Output                                         |  |  |

| H8      | VLDO5          | AO     | LDO5 Output                                         |  |  |

| J8      | VLDO6          | AO     | LD06 Output                                         |  |  |

| J11     | VLDO7          | AO     | LDO7 Output                                         |  |  |

| H12     | VLDO8          | AO     | LDO8 Output                                         |  |  |

| E12     | VLDO9          | AO     | LDO9 Output                                         |  |  |

| C12     | VLDO10         | AO     | LDO10 Output                                        |  |  |

| E9      | VLDO11         | AO     | LDO11 Output                                        |  |  |

| F9      | VLDO12         | AO     | LDO12 Output                                        |  |  |

| D11     | VLDO13         | AO     | LDO13 Output                                        |  |  |

| E8      | VLDO14         | AO     | LDO14 Output                                        |  |  |

| J9      | VLDO15         | AO     | LDO15 Output                                        |  |  |

| D8      | VLDO16         | AO     | LDO16 Output                                        |  |  |

| F11     | VLDO17         | AO     | LDO17 Output                                        |  |  |

| G12     | VLDO18         | AO     | LDO18 Output                                        |  |  |

| F8      | VLDO19         | AO     | LDO19 Output                                        |  |  |

| G11     | VLDO20         | AO     | LDO20 Output                                        |  |  |

| G9      | VLDO21         | AO     | LDO21 Output                                        |  |  |

| H9      | VLDO22         | AO     | LDO22 Output                                        |  |  |

| · I     |                | •      |                                                     |  |  |

| Pin No.  | Symbol                | I/O   | Description                      |  |  |  |

|----------|-----------------------|-------|----------------------------------|--|--|--|

| F12      | VLDO23                | AO    | LDO23 Output                     |  |  |  |

| G8       | VLDO24                | AO    | LDO24 Output                     |  |  |  |

| D12      | VLDO25                | AO    | LDO25 Output                     |  |  |  |

| B11      | VLDO26                | AO    | LDO26 Output                     |  |  |  |

| C11      | VLDO27                | AO    | LDO27 Output                     |  |  |  |

| D9       | VLDO28                | AO    | LDO28 Output                     |  |  |  |

| A10      | VBAT                  | Power | Power Supply for BGR             |  |  |  |

| A11      | VREF                  | AO    | Bandgap Reference Output         |  |  |  |

| Buck Cor | nverter Section       |       |                                  |  |  |  |

| M2       | VINB1                 | Power | Power Supply for Buck 1          |  |  |  |

| L1       | SW1                   | AO    | Switching Node of Buck 1         |  |  |  |

| K2       | FB1                   | AI    | Feedback of Buck1                |  |  |  |

| K1       | GNDB1                 | GND   | Power Ground for Buck 1          |  |  |  |

| L2       | VINB2                 | Power | Power Supply for Buck 2          |  |  |  |

| L3       | VINB2                 | Power | Power Supply for Buck 2          |  |  |  |

| M3       | VINB2                 | Power | Power Supply for Buck 2          |  |  |  |

| L4       | SW21                  | AO    | Switching Node of Buck 2         |  |  |  |

| M4       | SW21                  | AO    | Switching Node of Buck 2         |  |  |  |

| L5       | SW22                  | AO    | Switching Node of Buck 2         |  |  |  |

| M5       | SW22                  | AO    | Switching Node of Buck 2         |  |  |  |

| K3       | SI <sub>FB2</sub> OIA |       | Feedback of Buck 2               |  |  |  |

| K6       | GNDB21                | GND   | Power Ground for Buck 2          |  |  |  |

| L6       | GNDB22                | GND   | Power Ground for Buck 2          |  |  |  |

| M6       | GNDB23                | GND   | Power Ground for Buck 2          |  |  |  |

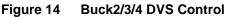

| K4       | RS2P                  | AIO   | Remote sensing of Buck 2 voltage |  |  |  |

| K5       | RS2N                  | AIO   | Remote sensing of Buck 2 GND     |  |  |  |

| J1       | VINB31                | Power | Power Supply for Buck 3          |  |  |  |

| J2       | VINB32                | Power | Power Supply for Buck 3          |  |  |  |

| H1       | SW31                  | AO    | Switching Node of Buck 3         |  |  |  |

| H2       | SW32                  | AO    | Switching Node of Buck 3         |  |  |  |

| G3       | FB3                   | AI    | Feedback of Buck3                |  |  |  |

| G1       | GNDB31                | GND   | Power Ground for Buck 3          |  |  |  |

| G2       | GNDB32                | GND   | Power Ground for Buck 3          |  |  |  |

| H3       | RS3P                  | AIO   | Remote sensing of Buck 3 voltage |  |  |  |

| J3       | RS3N                  | AIO   | Remote sensing of Buck 3 GND     |  |  |  |

| B2       | VINB4                 | Power | Power Supply for Buck 4          |  |  |  |

| C1       | VINB4                 | Power | Power Supply for Buck 4          |  |  |  |

| Pin No. | Symbol | I/O   | Description                          |  |  |  |

|---------|--------|-------|--------------------------------------|--|--|--|

| C2      | VINB4  | Power | Power Supply for Buck 4              |  |  |  |

| D1      | SW41   | AO    | Switching Node of Buck 4             |  |  |  |

| D2      | SW41   | AO    | Switching Node of Buck 4             |  |  |  |

| E1      | SW42   | AO    | Switching Node of Buck 4             |  |  |  |

| E2      | SW42   | AO    | Switching Node of Buck 4             |  |  |  |

| C3      | FB4    | AI    | Feedback of Buck 4                   |  |  |  |

| F1      | GNDB41 | GND   | Power Ground for Buck 4              |  |  |  |

| F2      | GNDB42 | GND   | Power Ground for Buck 4              |  |  |  |

| F3      | GNDB43 | GND   | Power Ground for Buck 4              |  |  |  |

| D3      | RS4P   | AIO   | Remote sensing of Buck 4 voltage     |  |  |  |

| E3      | RS4N   | AIO   | Remote sensing of Buck 4 GND         |  |  |  |

| B6      | VINB5  | Power | Power Supply for Buck 5              |  |  |  |

| A5      | SW5    | AO    | Switching Node of Buck 5             |  |  |  |

| B5      | FB5    | AIO   | Feedback of Buck 5                   |  |  |  |

| A4      | GNDB51 | GND   | Power Ground for Buck 5              |  |  |  |

| B4      | GNDB52 | GND   | Power Ground for Buck 5              |  |  |  |

| B1      | VINB6  | Power | Power Supply for Buck 6              |  |  |  |

| A2      | SW6    | AO    | Switching Node of Buck 6             |  |  |  |

| B3      | FB6    | A     | Feedback of Buck 6                   |  |  |  |

| A3      | GNDB6  | GND   | Power Ground for Buck 6              |  |  |  |

| A6      | SVINB7 | Power | Power Supply for Buck 7              |  |  |  |

| A7      | SW7    | AO    | Switching Node of Buck 7             |  |  |  |

| B7      | FB7    | AI    | Feedback of Buck 7                   |  |  |  |

| A8      | GNDB7  | GND   | Power Ground for Buck 7              |  |  |  |

| M10     | VINB8  | Power | Power Supply for Buck 8              |  |  |  |

| M11     | SW8    | AO    | Switching Node of Buck 8             |  |  |  |

| L10     | FB8    | AI    | Feedback of Buck 8                   |  |  |  |

| L12     | GNDB8  | GND   | Power Ground for Buck 8              |  |  |  |

| M9      | VINB9  | Power | Power Supply for Buck 9              |  |  |  |

| M8      | SW9    | AO    | Switching Node of Buck 9             |  |  |  |

| L9      | FB9    | AI    | Feedback of Buck 9                   |  |  |  |

| M7      | GNDB9  | GND   | Power Ground for Buck 9              |  |  |  |

| L7      | DS2    | DI    | DVS Selection for Buck 2             |  |  |  |

| K7      | DS3    | DI    | DVS Selection for Buck 3             |  |  |  |

| K8      | DS4    | DI    | DVS Selection for Buck 4             |  |  |  |

| C5      | DVS1   | DI    | Output Voltage Setting for Buck2/3/4 |  |  |  |

| D5      | DVS2   | DI    | Output Voltage Setting for Buck2/3/4 |  |  |  |

| Pin No. | Symbol | I/O | Description                          |

|---------|--------|-----|--------------------------------------|

| E5      | DVS3   | DI  | Output Voltage Setting for Buck2/3/4 |

**NOTE:** Power, GND: Power Supply.

AI, AO, AIO: Analog Input, Output, Input/Output. DI, DO, DIO: Digital Input, Output, Input/Output.

SAMSUNG ELECTRONICS

#### **1.6 Absolute Maximum Ratings**

| Characteristic                 | Symbol                                                     | Value        | Unit |

|--------------------------------|------------------------------------------------------------|--------------|------|

| Maximum Battery Supply Voltage | VBAT                                                       | – 0.3 to 6.0 | V    |

| Maximum Analog Supply Voltage  | VINB1 to VINB9, VINL1 to<br>VINL9, VDD_CP32K,<br>VDD_BT32K | – 0.3 to 6.0 | V    |

| Junction Temperature           | TJ                                                         | – 40 to 150  | °C   |

| Storage Temperature            | T <sub>STG</sub>                                           | – 55 to 150  | °C   |

**NOTE:** ABSOLUTE MAXIMUM RATING specifies the values beyond which the device may be damaged permanently. Exposure to ABSOLUTE MAXIMUM RATING conditions for extended periods may affect reliability. Each condition value is applied with the other values kept within the following operating conditions and function operation under any of these conditions is not implied.

#### **1.7 Recommended Operating Condition**

| Characteristic                           | Symbol                            | Value                | Unit |

|------------------------------------------|-----------------------------------|----------------------|------|

| Battery Supply Voltage                   | VBAT                              | 2.65 (TBD) to<br>5.5 | V    |

| Analog Supply Voltage                    | VINB1 to VINB9, VINL4 to<br>VINL7 | 2.65 (TBD) to<br>5.5 | V    |

|                                          | VDD_CP32K, VDD_BT32K              | 1.0 to 5.5           | V    |

| Analog Supply Voltage for Sub-Regulation | VINL1, VINL2, VINL3, 20           | 1.7 to 5.5           | V    |

| Analog Supply Voltage for Sub-Regulation | VINL8, VINL9                      | 1.0 to 5.5           | V    |

| Operating Ambient Temperature            | T <sub>OPR</sub>                  | – 40 to 85           | °C   |

#### SAMSUNG ELECTRONICS

# **2** Electrical Specifications

#### 2.1 General and Logic

| Characteristics                           | Test Conditions                                                                                                                                          | Min. | Тур.         | Max. | Unit |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|------|------|

| Supply Current                            |                                                                                                                                                          |      |              |      | •    |

| Shutdown supply current                   | All Bucks and LDOs are off.<br>Backup battery is fully charged.                                                                                          | _    | 10           |      | μA   |

| No load current 1 (Sleep Mode)            | LDO1,5,13,17 & Buck 5<br>Low Power Mode, LDO3 Normal<br>Mode, Buck 7 On,<br>(PWREN = Low)<br>Backup battery is fully charged.<br>Other circuits are off. | _    | 120<br>(TBD) |      | μΑ   |

| No load current 2 (Default On)            | Buck1,2,3,4,5,7,8, LDO1-3, 5-8,10-<br>17 on.<br>Backup battery is fully charged.<br>Other circuits are off.                                              | N    | 600          | 1000 | μΑ   |

| UVLO and VREF                             | leff cui at 14·14                                                                                                                                        | 2011 | 121          | 3    |      |

| Under-voltage lockout threshold           | UVLO rising                                                                                                                                              | ,    | 3.1          | -    | V    |

| Under-vollage lockout threshold           | UVLO falling                                                                                                                                             | -    | 2.55         | -    | V    |

| Reference voltage (VREF)                  | VBATT = 2.65 V to 5.5 V                                                                                                                                  | -    | 0.8          | -    | V    |

| VREF capacitor                            |                                                                                                                                                          | -    | 100          | -    | nF   |

| Thermal Shutdown                          |                                                                                                                                                          |      |              |      |      |

| Thermal chutdown temperature              | Thermal shutdown threshold                                                                                                                               | -    | 160          | -    | °C   |

| Thermal shutdown temperature              | Thermal shutdown hysteresis                                                                                                                              | -    | 20           | -    | °C   |

| Power Management                          |                                                                                                                                                          |      |              |      |      |

|                                           | Power on Key input                                                                                                                                       | 1.4  | _            | -    | V    |

| PWRON                                     | Pull-down input resistor,<br>Connected to AGND                                                                                                           | -    | 800          | _    | kΩ   |

| MRB1/2                                    | Reset Key input                                                                                                                                          | -    | _            | 0.4  | V    |

| PWREN                                     | Power enable input                                                                                                                                       | 1.4  | _            | _    | V    |

| PWRHOLD                                   | Power supply hold input                                                                                                                                  | 1.4  | _            | _    | V    |

| DVS1, DVS2, DVS3, DS2,                    | Logic input low level                                                                                                                                    | _    | _            | 0.4  | V    |

| DS3, DS4, B5S1, B5S2,<br>LDO4EN, LDO18EN, | Logic input high level                                                                                                                                   | 1.4  | _            | _    | V    |

SAMSUNG ELECTRONICS

| Characteristics                             | Test Conditions                                                    | Min.    | Тур.                              | Max.     | Unit |

|---------------------------------------------|--------------------------------------------------------------------|---------|-----------------------------------|----------|------|

| LDO23EN, BUCK6EN,<br>BUCK9EN, JIGONB, ACOKB |                                                                    |         |                                   |          |      |

|                                             | Logic input low level from AP                                      | _       | _                                 | 0.4      | V    |

| SCL, SDA input                              | Logic input high level from AP                                     | 1.4     | _                                 | _        | V    |

| (I2C Control Signals)                       | Logic input hysteresis                                             | _       | 0.2                               | -        | V    |

|                                             | Logic input coupling capacitor                                     | _       | _                                 | 10       | pF   |

| SDA Output (I2C Output Signal)              | SDA logic output low signal,<br>NMOS open drain output, active low | Pull-up | external res<br>LDO3              | istor to | V    |

|                                             | Logic output to AP, active low                                     | _       | _                                 | 0.2      | V    |

|                                             | System reset output signal,<br>NMOS open-drain output              | Pull-up | Pull-up external resistor to LDO3 |          | V    |

| ONOB,RSOB, IRQB                             | Logic output to AP, active low                                     | _       | _                                 | 0.2      | V    |

|                                             | RSOB De-assert delay                                               | _       | 60                                | _        | ms   |

| I2C Control                                 |                                                                    |         |                                   |          |      |

| Clock frequency                             | _                                                                  | _       | _                                 | 3.5      | MHz  |

| Bus free time between start and stop        | _                                                                  | 1.3     | _                                 | _        | μs   |

| Hold time repeated start condition          | ARACII                                                             | 0.6     |                                   | _        | μS   |

| CLK low period                              |                                                                    | 1.3     |                                   | —        | μS   |

si - plaza / Jeff\_cui at 14:14,2011.12.13

SAMSUNG ELECTRONICS

#### **2.2 Buck Converters**

#### 2.2.1 Buck Converter 1, 3, 5, 6, 7, 8, 9

#### (VBAT = 3.7 V, $T_A$ = 25 °C, unless otherwise specified) Buck 1, 3, and 5 to 9: Cout = 10 $\mu$ F, L = 1.0 $\mu$ H

| Characteristics               |                           | Test Condition               | าร           |       | Min.    | Тур.  | Max.    | Unit   |  |

|-------------------------------|---------------------------|------------------------------|--------------|-------|---------|-------|---------|--------|--|

| Voltage Mode Buck Co          | onverter                  |                              |              |       |         |       |         |        |  |

| Input voltage range (1)       |                           |                              |              |       | 2.7     |       | 5.5     | V      |  |

| Shutdown current (2)          | Regulator                 | <sup>r</sup> disabled        |              |       | _       | 0.1   | _       | μA     |  |

| Ground current <sup>(2)</sup> | Buck<br>1,3,5,6,<br>7,8,9 | Regulator enabled switching, | , no load, r | 10    | -       | 17    | -       | μΑ     |  |

|                               | Buck5                     | Low power mode               |              |       |         | 10    |         |        |  |

|                               | Buck 1, p                 | rogrammable in 6.25          | 5 mV Steps   | ;     | 0.650   |       | 2.225   |        |  |

|                               | Buck 3, p                 | rogrammable in 6.25          | 5 mV Steps   | ;     | 0.600   |       | 1.6     |        |  |

|                               | Buck 5, p                 | rogrammable in 6.25          | 5 mV Steps   | ;     | 0.650   |       | 2.225   |        |  |

| Output voltage range          | Buck 6, p                 | rogrammable in 6.25          | 5 mV Steps   | ;     | 0.650   |       | 2.225   | V      |  |

|                               | Buck 7, p                 |                              |              | 0.750 |         | 3.000 |         |        |  |

|                               | Buck 8, p                 |                              |              | 0.750 |         | 3.000 |         |        |  |

|                               | Buck 9, p                 | rogrammable in 12.5          | 5 mV Steps   | ;     | 0.750   |       | 3.300   |        |  |

|                               | Buck 1                    | PWM Mode                     |              |       | - 3.0 % | 1.0   | + 3.0 % |        |  |

|                               | Buck 3                    | PWM Mode                     |              | 4.4   | – 1.0 % | 1.0   | + 1.0 % |        |  |

|                               | IZA /                     | PWM Mode &                   | 1114.        | 00    | - 3.0 % | 1.2   | + 3.0 % |        |  |

|                               | Duals C                   | lload < 5 mA                 | B5S1 &       | 01    | - 3.0 % | 1.35  | + 3.0 % |        |  |

| Default output voltage        | Buck 5                    | (Low power                   | B5S2<br>(4)  | 10    | - 3.0 % | 1.50  | + 3.0 % | .,     |  |

| (5)                           |                           | mode)                        |              | 11    | - 3.0 % | 1.80  | + 3.0 % | V      |  |

|                               | Buck 6                    | PWM Mode                     |              | •     | - 3.0 % | 1.2   | + 3.0 % |        |  |

|                               | Buck 7                    | PWM Mode                     |              |       | - 3.0 % | 2.0   | + 3.0 % |        |  |

|                               | Buck 8                    | PWM Mode                     |              |       | - 3.0 % | 1.4   | + 3.0 % |        |  |

|                               | Buck 9                    | PWM Mode                     |              |       | - 3.0 % | 2.85  | + 3.0 % |        |  |

|                               | Buck 1, 6                 | , 7, 8, 9                    |              |       | 1500    | _     | _       |        |  |

| Maximum output                | Buck 3                    |                              |              |       | 2500    | _     | _       |        |  |

| current                       |                           | Normal mode                  |              |       | 2000    | _     | _       | mA     |  |

|                               | Buck 5                    | Low power mode               |              |       | 5       |       |         |        |  |

| Output load regulation        | Buck 1,<br>6, 7, 8,<br>9  | 10mA < lout < 1.5            | A (PWM)      |       | _       | 0.15  | -       | %/A    |  |

| e apar load rogulation        | Buck 3                    | 10mA < lout < 2.5            | A (PWM)      |       | -       | 0.15  | -       | ,0,7 ( |  |

|                               | Buck 5                    | 10mA < lout < 2.0            | A (PWM)      |       | _       | 0.15  | _       |        |  |

SAMSUNG ELECTRONICS

| Characteristics                            |                        | Test Conditions                                                                                                                                             |      | Тур. | Max. | Unit      |

|--------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------|

| Output line regulation                     | VINBx = 3              | VINBx = 3.0 V to 4.5 V                                                                                                                                      |      | 0.1  | -    | %/V       |

|                                            | Buck 1                 | PFET Switch                                                                                                                                                 | -    | 2200 | -    |           |

|                                            | Buck 3                 | PFET switch                                                                                                                                                 | _    | 3700 | -    |           |

|                                            | Buck 5                 | PFET switch                                                                                                                                                 | _    | 3000 | -    |           |

| Current limit                              | Buck 6                 | PFET switch                                                                                                                                                 | _    | 2200 | -    | mA        |

|                                            | Buck 7,<br>8           | PFET switch                                                                                                                                                 | _    | 2200 | _    |           |

|                                            | Buck 9                 | PFET switch                                                                                                                                                 | _    | 2200 | _    |           |

|                                            | Buck 1,                | PFET switch (VINB to SW), ILX =<br>- 150 mA @3.7 V                                                                                                          | _    | 150  | -    |           |

|                                            | 5, 6, 7,<br>8, 9       | NFET rectifier (SW to GNDB), ILX<br>= - 150 mA @3.7 V                                                                                                       | -    | 80   | -    |           |

| On-resistance                              |                        | PFET switch (VINB to SW), ILX =<br>- 50 mA @3.7 V                                                                                                           | -    | 130  | -    | - mΩ      |

|                                            | Buck 3                 | NFET rectifier (SW to GNDB), ILX<br>= - 150 mA @3.7 V                                                                                                       | -    | 70   | -    |           |

| Switching frequency                        | PWM mo                 | de                                                                                                                                                          | _    | 3.5  | _    | MHz       |

| A stille discharge                         | Regulator<br>GNDB3 for | disabled, resistance from FB3 to<br>or Buck 3                                                                                                               | -    | 0.1  | _    | 1.0       |

| Active discharge                           | U U                    | disabled, resistance from SWx to<br>or Buck 1, 5, 6, 7, 8, 9                                                                                                |      | 1    |      | - kΩ      |

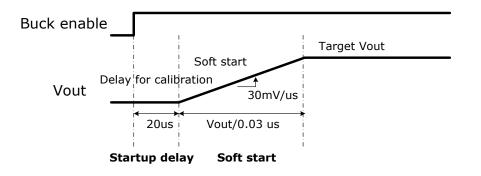

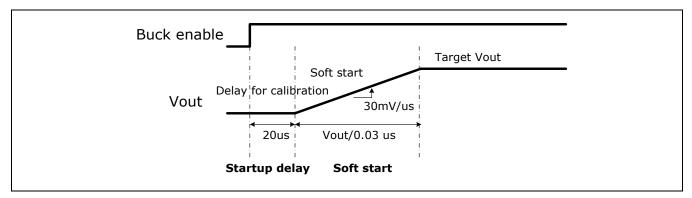

| Soft start ramp rate (3)                   | Ramp rat               | e in soft start operation 14 14                                                                                                                             | 2011 | 30   | 13-  | mV/<br>μs |

| Startup delay <sup>(3)</sup>               | Delay for              | calibration                                                                                                                                                 |      | 20   |      | μS        |

| Dynamic-change ramp<br>Rate <sup>(2)</sup> | Buck 3                 | Positive and Negative Ramp Rate<br>in Dynamic Voltage Scale<br>5 mV/μs,10 mV/μs, 25 mV/μs, 50<br>mV/μs and 100 mV/μs<br>Ramp off: Max ramp rate (100<br>mV) | 5    | 10   | 100  | mV/μs     |

#### 2.2.2 Buck Converter 2 & 4

(VBAT = 3.7 V,  $T_A$  = 25 °C, unless otherwise specified) Buck 2, 4: Cout = 2x10  $\mu$ F, L = 1.0  $\mu$ H

| Characteristics                            |                           | Test Conditions                                                                                                                                                     | Min.    | Тур. | Max.    | Unit  |

|--------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|---------|-------|

| Current Mode Buck Con                      | verter                    |                                                                                                                                                                     |         |      |         |       |

| Input voltage range (1)                    |                           |                                                                                                                                                                     | 2.7     |      | 5.5     | V     |

| Shutdown current <sup>(2)</sup>            | Regulator d               | Regulator disabled                                                                                                                                                  |         | 0.1  | _       | μA    |

|                                            | Regulator e               | nabled, no load, no switching,                                                                                                                                      | _       | 22   | _       |       |

| Ground current <sup>(2)</sup>              | No load, No<br>Sensing mo | switching current In Remote                                                                                                                                         |         | 32   |         | μA    |

| Output voltage range                       | Programma                 | ble in 6.25 mV Steps                                                                                                                                                | 0.6     |      | 1.6     | V     |

| Default output voltage                     | Buck 2                    | PWM Mode                                                                                                                                                            | – 1.0 % | 1.1  | + 1.0 % | V     |

| (5)                                        | Buck 4                    | PWM Mode                                                                                                                                                            | – 1.0 % | 1.0  | + 1.0 % | V     |

| Maximum output current                     | Maximum C                 | Dutput current                                                                                                                                                      | 5000    | _    | _       | mA    |

| Output load regulation                     | Buck 2, 4                 | 10 mA < lout < 5.0 A<br>(PFM to PWM)                                                                                                                                | _       | 0.5  | _       | %/A   |

| Output line regulation                     | Buck 2, 4                 | VINBx = 3.0 V to 4.5 V                                                                                                                                              | _       | 0.1  | _       | %/V   |

| Current limit                              | Buck 2, 4                 | PFET Switch                                                                                                                                                         |         | 6000 | _       | mA    |

|                                            | $\mathbf{D}\mathbf{A}$    | PFET switch (VINBx to SWx),<br>ILX = $-150 \text{ mA } @3.7 \text{ V}$                                                                                              |         | 150  | _       |       |

| On-resistance<br>SI - pla                  | Buck 2, 4<br>Za / J       | NFET rectifier (SWx to<br>GNDBx), ILX = - 150 mA<br>@3.7 V                                                                                                          | ,201    | 802  | 13-     | mΩ    |

| Switching frequency                        | Buck 2, 4                 | PWM MODE                                                                                                                                                            | _       | 2.5  | 3.0     | MHz   |

| Active discharge                           | Regulator d<br>GNDBx      | isabled, resistance from FBx to                                                                                                                                     | _       | 50   | -       | Ω     |

| Soft start ramp rate (3)                   | Ramp rate i               | n soft start operation                                                                                                                                              | _       | 30   | _       | mV/μs |

| Startup delay <sup>(3)</sup>               | Delay for ca              | alibration                                                                                                                                                          |         | 20   |         | μS    |

| Dynamic-change ramp<br>rate <sup>(2)</sup> | Buck 2, 4                 | Positive and Negative Ramp<br>Rate with 5 mV/µs,10 mV/µs,<br>25 mV/µs, 50 mV/µs and 100<br>mV/µs in Dynamic Voltage<br>Scale<br>Ramp off: Max ramp rate (100<br>mV) | 5       | 10   | 100     | mV/μs |

#### NOTE:

1. Minimum input voltage is 1/Dmax multiplied by the addition of output voltage and the product of load current and sum of Ron and Rparasitic.

- 2. Design guidance; not tested for each device.

- 3. Startup waveform of Buck converter.

SAMSUNG ELECTRONICS

27

- 4. B5S1 / B5S2 control output voltage of Buck5 and LDO2 together.

- 5. PFM voltage is 10mV higher than PWM voltage.

#### 2.3 LDOs

#### 2.3.1 LDO (P) 4, 5, 11, 12, 13, 14, 16, 17, 19, 20, 21, 22, 26, 27, 28 (150 mA, PMOS)

| (VBAT = 3.7 V, $T_A$ = 25 °C, unless otherwise |

|------------------------------------------------|

|------------------------------------------------|

| Characteristics                              | Test Conditions                                |                                                                      | Min. | Тур.  | Max. | Unit |

|----------------------------------------------|------------------------------------------------|----------------------------------------------------------------------|------|-------|------|------|

| Input voltage range<br>(VINL) <sup>(1)</sup> |                                                |                                                                      | 1.7  | -     | 5.5  | V    |

| Under voltage Lockout                        | Rising, 100 mV Hyste                           | eresis                                                               |      | 1.6   | 1.7  | V    |

| Battery Voltage Range                        | Equal or Higher than                           | VINL                                                                 | 2.7  | _     | 5.5  | V    |

| Output Voltage Range                         | IL = 150 mA<br>Programmable in 50              | mV steps                                                             | 0.8  | _     | 3.95 | V    |

| Default output voltage<br>(VLDO)             | LDO (P) 4, 5, 11,<br>13, 14, 16, 26, 27,<br>28 |                                                                      |      | 1.8   |      |      |

|                                              | LDO (P) 17                                     | 150 mA @VINL                                                         | _    | 2.8   | _    | V    |

|                                              | LDO (P) 12, 19, 20,<br>21                      | = VLDO +0.3V                                                         |      | 3.0   |      |      |

|                                              | LDO (P) 22                                     |                                                                      |      | 3.3   |      |      |

| Maximum Load                                 | Normal Mode                                    | Normal Mode                                                          |      |       |      |      |

| Current                                      | Low-Power Mode                                 |                                                                      | 5    |       |      | mA   |

| Output Current Limit                         | VOUT = 90 % of VLDO                            |                                                                      | 180  | 225   | 270  | mA   |

| Minimum Output<br>Bypass Capacitance         | zo / loff /                                    | oui ot 14:14                                                         | 0.7  | 1     | 12   | μF   |

| 51 - pic                                     | Battery Supply<br>Current, with No             | Shutdown                                                             | 2011 | < 0.1 | 10   |      |

|                                              |                                                | Normal Regulation                                                    |      | 8     | 10   |      |

|                                              | Load                                           | Low-Power Mode                                                       |      | 0.5   | 1    |      |

|                                              | Input Supply<br>Current, with No               | Shutdown                                                             |      | 0     | 1    | μΑ   |

| Ground Current                               |                                                | Normal Regulation                                                    |      | 12    | 20   |      |

|                                              | Load                                           | Low-Power Mode                                                       |      | 2     | 5    |      |

|                                              | Normal Mode Total C                            | Current                                                              |      | 20    | 30   |      |

|                                              | Low-Power Mode To                              | tal Current                                                          |      | 2.5   | 6    |      |

|                                              | LDO disabled Total C                           | Current                                                              |      | < 0.1 |      |      |

| Output voltage<br>accuracy                   | Normal Mode                                    | VINL = VLDO + 0.3 V<br>to 5.5 V,<br>IL = 0.1 mA to 150 mA.           | - 3  | _     | + 3  | 0/   |

|                                              | Low power Mode                                 | VINL = VLDO + 0.3 V<br>to 5.5 V,<br>IL = 0.1 mA to 5 mA,             | - 3  |       | + 3  | %    |

| Load Regulation <sup>(2)</sup>               | Normal Mode                                    | VINL = VLDO + 0.3 V,<br>VBAT = VLDO +1.5 V,<br>IL = 0.1 mA to 150 mA |      | 0.1   |      | %    |

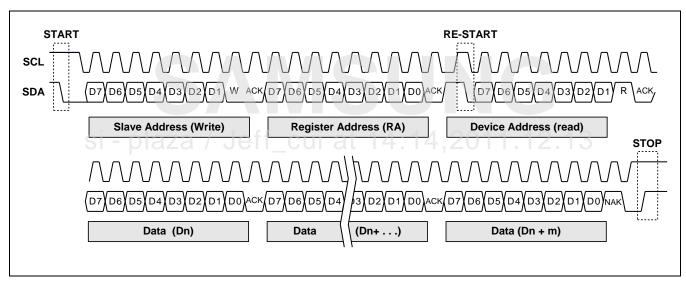

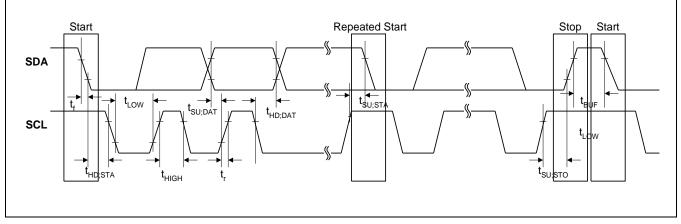

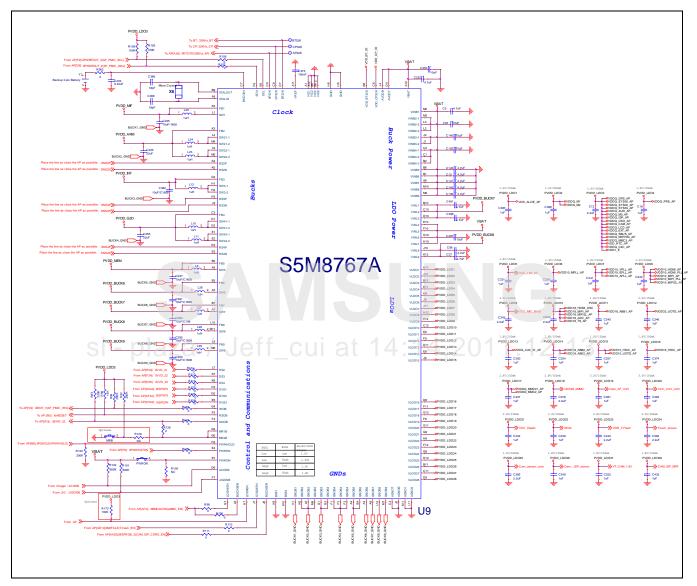

SAMSUNG ELECTRONICS